| Indeks | English version |

Na tej stronie opisane są tylko szczegóły charakterystyczne dla PB-2000C. Ogólniejsze informacje na temat mikroprocesora i magistrali są dostępne w opisie sprzętu PB-1000.

CS0: &H10000..&H17FFF, wewnętrzna pamięć RAM 32kB

CS1: &H18000..&H1FFFF, wewnętrzne rozszerzenie pamięci RAM 32kB oraz domyślny zakres adresów dla modułu rozszerzenia pamięci RP-33 (otwarta zworka 4, zalutowana zworka 5)

CS2: &H28000..&H3FFFF, alternatywny zakres adresów wybierający moduł RP-33 (gdy jest otwarta zworka 5 a zalutowana zworka 4)

CS3: &H30000..&H3FFFF, nie używane

CS4: &H00D90..&H0FFFF, nie używane

CS5: &H04000..&H05FFF, złącze dodatkowych urządzeń

CS6: &H00C10..&H00C11, gate array (rejestry konfiguracji pamięci)

CS7: &H00C00..&H00C0F, gate array (wyłączone adresy), interfejs portu szeregowego, drukarki i stacji dysków elastycznych

P7..P6 sterują głośniczkiem piezoelektrycznym

P5 jest wyjściem reset dla urządzeń peryferyjnych

P4 załącza zasilanie interfejsu FDD, 0 gdy włączone

P3 wybiera kierunek transferu FDD, 1 gdy zapis do interfejsu FDD, 0 gdy odczyt z interfejsu FDD

P2 jest wejściem sygnału potwierdzenia wyboru kierunku transmisji interfejsu FDD

P1 wykrywa obecność karty (niski poziom napięcia gdy karta jest włożona)

P0 wybiera wersję językową, może być połączony za pomocą zworki do VSS (wersja angielska PB-2000C) lub GND (wersja japońska AI-1000)

| Końcówka | Symbol | Funkcja |

|---|---|---|

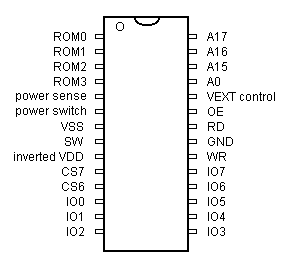

| 1 | ROM0 | wyjście chip select wybierające wbudowaną pamięć ROM z interpreterem języka C, aktywny niski poziom, dekoduje zakres adresów &H00000..&H0FFFF z wyłączeniem segmentów dekodowanych przez wyjścia ROM2 i ROM3 |

| 2 | ROM1 | nie używane, dekoduje stały zakres adresów &H10000..&H2FFFF |

| 3 | ROM2 | steruje końcówką 20 złącza karty pamięci, dekodowany zakres adresów zależy od rejestru &H00C10 |

| 4 | ROM3 | steruje końcówką 33 złącza karty pamięci, dekodowany zakres adresów zależy od rejestru &H00C11 |

| 5 | power sense | dostaje wysoki poziom napięcia z układu monitora baterii S8054ALR gdy obecne jest prawidłowe napięcie zasilające |

| 6 | power switch | dostaje niski poziom napięcia gdy wyłącznik jest w pozycji ON oraz zatrzaśnięta karta pamięci |

| 7 | VSS | minus zasilania |

| 8 | SW | wyjście steruje końcówką mikroprocesora 36, niski poziom napięcia załącza system |

| 9 | inverted VDD | wejście odczytujące stan końcówki mikroprocesora 33 poprzez inwerter zbudowany na tranzystorze pnp |

| 10 | CS7 | niski poziom napięcia na tym wejściu blokuje sygnały ROM0..ROM3, służy do pominięcia z przestrzeni adresowej zakresu adresów &H00C00..&H00C0F zajętych przez interfejs FA-7/FD-100 |

| 11 | CS6 | wejście chip enable dla rejestrów konfiguracji pamięci, dostaje niski poziom z CPU w zakresie adresów &H00C10..&H00C11, niski poziom na tym wejsciu blokuje sygnały ROM0..ROM3 |

| 12..19 | IO0..IO7 | dwukierunkowa szyna danych |

| 20 | WR | sygnał strobu zapisu, aktywny niski poziom |

| 21 | GND | plus zasilania |

| 22 | RD | sygnał strobu odczytu, aktywny niski poziom |

| 23 | OE | sygnalizuje ważne dane |

| 24 | VEXT control | niski poziom na tym wyjściu załącza zasilanie wyświetlacza LCD |

| 25..28 | A0, A15..A17 | szyna adresowa |

| bit rejestru | dekodowana kombinacja bitów adresu | dekodowany zakres adresów |

|---|---|---|

| 0 1 2 3 4 5 6 7 |

A17..A15 = 000 A17..A15 = 001 A17..A15 = 010 A17..A15 = 011 A17..A15 = 100 A17..A15 = 101 A17..A15 = 110 A17..A15 = 111 |

&H00000..&H07FFF &H08000..&H0FFFF &H10000..&H17FFF &H18000..&H1FFFF &H20000..&H27FFF &H28000..&H2FFFF &H30000..&H37FFF &H38000..&H3FFFF |

Rzeczywisty dekodowany zakres adresów pierwszego segmentu pamięci jest ograniczony do &H00C12..&H07FFF. Adresy &H00C00..&H00C11 są wykluczone, a CPU nigdy nie umieszcza adresów poniżej &H00C00 na zewnętrznej szynie adresowej.

Ze względu na konflikt z pamięcią RAM w banku 1 nie należy ustawiać bitów 2 i 3 rejestru konfiguracji.

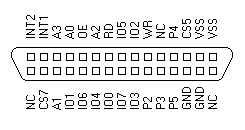

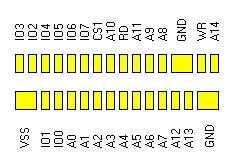

01 - VSS 16 - IO5 31 - A17 02 - A12 17 - IO6 32 - GND 03 - A7 18 - IO7 33 - ROM3 04 - A6 19 - GND 34 - GND 05 - A5 20 - ROM2 35 - GND 06 - A4 21 - A10 36 - NC 07 - A3 22 - RD 37 - NC 08 - A2 23 - A11 38 - NC 09 - A1 24 - A9 39 - NC 10 - A0 25 - A8 40 - NC 11 - IO0 26 - A13 41 - NC 12 - IO1 27 - WR 42 - NC 13 - IO2 28 - A14 43 - NC 14 - IO3 29 - A15 44 - P1 15 - IO4 30 - A16 45 - GND

pin 20 - ROM2 chip enable (gate array pin 3)

pin 33 - ROM3 chip enable (gate array pin 4)

pin 44 - port P1 mikroprocesora, wykrywa obecność karty, połączone z VSS wewnątrz karty

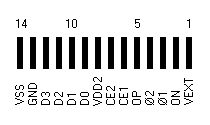

VEXT jest napięciem zasilającym wyświetlacz ok. -7V

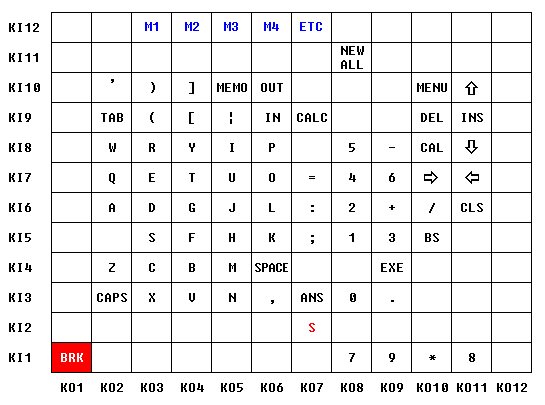

Kolumny matrycy klawiatury są wybierane przez 12-bitowy port wyjściowy KO, sterowany za pomocą rejestru IA. Wciśnięty klawisz łączy wybraną kolumnę z jednym z wierszy. Linie wierszy są odczytywane przez 12-bitowy port wejściowy KI, dostępny poprzez rejestr KY.

Relacja pomiędzy bitami rejestru KY a wierszami klawiatury:

![]()

GND jest plusem zasilania, VSS jest minusem zasilania.

GND jest plusem zasilania, VSS jest minusem zasilania.