| Indeks | English version |

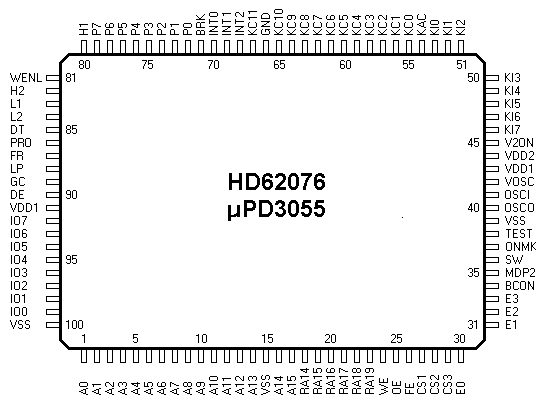

| Końcówka | Symbol | Funkcja |

|---|---|---|

| 1..14 | A0..A13 | szyna adresowa |

| 15 | VSS | minus zasilania |

| 16..17 | A14..A15 | szyna adresowa |

| 18..23 | RA14..RA19 | szyna adresowa |

| 24 | WE | sygnał strobu zapisu, aktywny niski poziom |

| 25 | OE | sygnał strobu odczytu, aktywny niski poziom |

| 26..29 | FE, CS1..CS3 | chip Enable, aktywny niski poziom CS3: pamięć RAM 64kB |

| 30..33 | E0..E3 | Chip Enable, aktywny niski poziom. E0: wewnętrzna pamięć ROM 128kB E2: karta pamięci, pin 20 E3: karta pamięci, pin 33 |

| 34 | BCON | |

| 35 | MDP2 | |

| 36 | SW | |

| 37 | ONMK | |

| 38 | TEST | |

| 39 | VSS | minus zasilania |

| 40,41 | OSCO, OSCI | rezonator ceramiczny 2.01MHz, OSCO jest wyjściem inwertera oscylatora |

| 42 | VOSC | zasilanie oscylatora |

| 43,44 | VDD1, VDD2 | plus zasilania |

| 45 | V2ON | sygnał wyjściowy Power On |

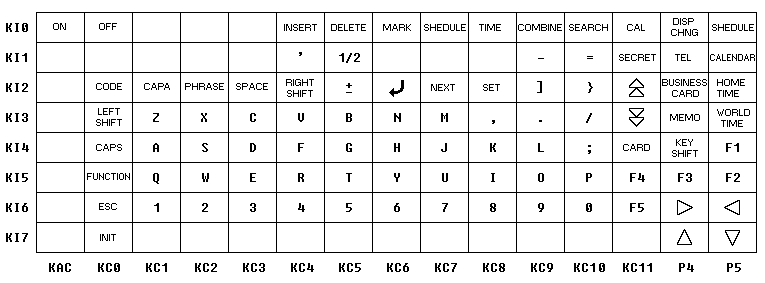

| 46..53 | KI7..KI0 | port wejściowy matrycy klawiatury, dostępny przez rejestr KY |

| 54..65 | KAC, KC0..KC10 | port wyjściowy matrycy klawiatury, sterowany przez rejestr KY |

| 66 | VSS | minus zasilania |

| 67 | KC11 | port wyjściowy matrycy klawiatury, sterowany przez rejestr KY |

| 68 | INT2 | wejście przerwań, sterowane z pin 28 układu HD62063 |

| 69 | INT1 | wejście przerwań, połączone razem z P01 (dane odbierane z portu szeregowego) |

| 70 | INT0 | wejście przerwań, połączone razem z P02 (stan wyłącznika zasilania) |

| 71 | BRK | |

| 72..79 | P0..P7 | 8-bitowy dwukierunkowy port dostępny przez rejestr PD Funkcja poszczególnych bitów portu: P1 odbiera dane z portu szeregowego P2 wejście sterowane z końcówki 14 gate array μPD65005, wysoki poziom gdy wyłącznik zasilania znajduje się w pozycji ON P3 wykrywa obecność karty (niski poziom napięcia gdy karta jest włożona) P4,P5 sterują dwoma liniami matrycy klawiatury |

| 80 | H1 | 4-bitowy port wyjściowy sterowany przez rejestr PE |

| 81 | WENL | połączone z VSS |

| 82..84 | H2, L1, L2 | 4-bitowy port wyjściowy sterowany przez rejestr PE L1: karta pamięci, pin 32 (wysoki poziom napięcia otwiera dostęp do pamięci RAM w karcie) |

| 85 86 87 88 89 90 | DT PRO FR LP GC DE |

sygnaly sterujące wyświetlacza |

| 91 | VDD1 | plus zasilania |

| 92..99 | IO7..IO0 | dwukierunkowa szyna danych |

| 100 | VSS | minus zasilania |

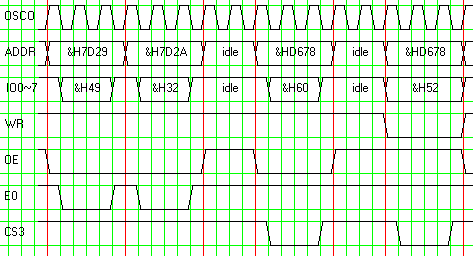

Wykres ilustruje przebiegi na magistrali systemowej zarejestrowane w czasie wykonywania następującej instrukcji:

7D29: 49 32 XR (IX),&H32

Kolumny matrycy klawiatury są wybierane przez 13-bitowy port wyjściowy KC oraz dwie linie 8-bitowego portu P0. Wciśnięty klawisz łączy wybraną kolumnę z jednym z wierszy. Linie wierszy są odczytywane przez 8-bitowy port wejściowy KI.

01 - VSS 16 - IO5 31 - A17 02 - A12 17 - IO6 32 - L1 03 - A7 18 - IO7 33 - E3 04 - A6 19 - VCC 34 - A18 05 - A5 20 - E2 35 - A19 06 - A4 21 - A10 36 - IO0 07 - A3 22 - RD 37 - IO1 08 - A2 23 - A11 38 - IO2 09 - A1 24 - A9 39 - IO3 10 - A0 25 - A8 40 - IO4 11 - IO0 26 - A13 41 - IO5 12 - IO1 27 - WR 42 - IO6 13 - IO2 28 - A14 43 - IO7 14 - IO3 29 - A15 44 - P03 15 - IO4 30 - A16 45 - VDD

pin 19 - VCC, napięcie zasilające obecne po włączeniu organizera

pins 36..43 - połaczone z 11..18

pin 44 - port P3 mikroprocesora, wykrywa obecność karty, połączone z VSS wewnątrz karty

pin 45 - VDD, napięcie zasilające obecne cały czas